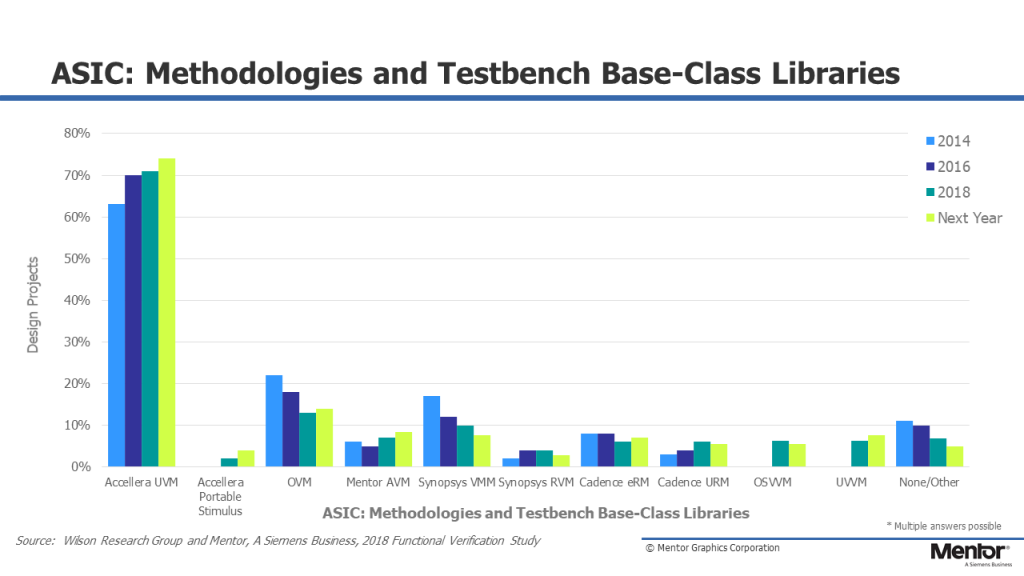

SystemVerilog and UVM are the current standards in SoC verification. UVM offers general conventions and ready building blocks for quick development of well-constructed and reusable verification environments on top of SystemVerilog language. Over 70% of ASIC verification in the industry is already done with UVM and the growth still continues [1].

PREREQUISITES You should have taken an elementary course on digital logic design and a course on register-transfer level (RTL) design and coding, or acquired equivalent skills. Also, some experience in object-oriented programming is recommended. If you know VHDL language and the keywords class, object, and constructor from Python or C++, you will probably do fine!

COURSE CONTENTS AND ORGANIZATION The course will teach you:

* motivation for SoC verification,

* the design and verification oriented sides of SystemVerilog language, and

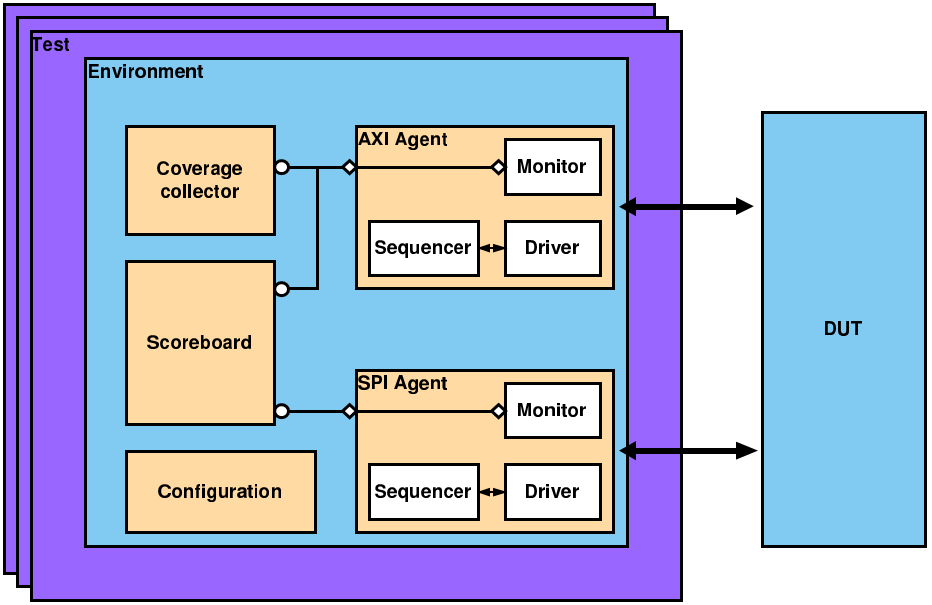

* UVM environment and test design.

The course consists of lectures, student seminar presentations and laboratory exercises. In the labs, you will create your own UVM environment and a coverage driven constrained random test for finding bugs in misbehaving designs. The course can be included in the master’s and post-graduate curriculum (5 credit points).

Sign up today to TIE-12206 2019-16, but at the latest by December 23 2019, since we can accommodate at most 32 students.

Course description in Study Guide.

If you are not studying at Tampere University at the moment, you can enroll via Open university.

If you have questions, contact: arto.oinonen@tuni.fi

[1] Foster, H. “The 2018 Wilson Research Group Functional Verification Study”. Verification Horizons Blog (2019). Available: https://blogs.mentor.com/verificationhorizons/blog/2018/11/14/prologue-the-2018-wilson-research-group-functional-verification-study/