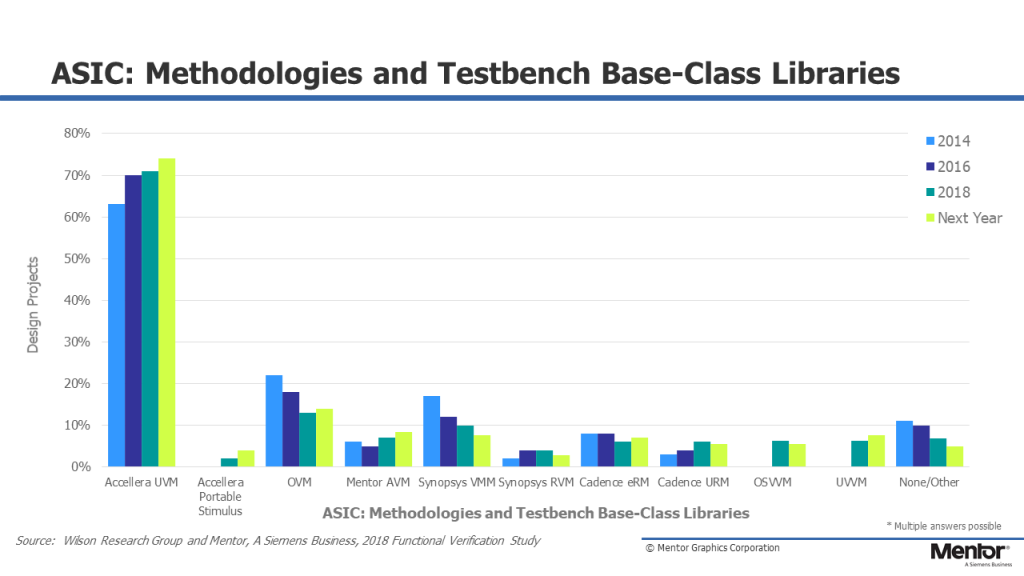

SystemVerilog and UVM are the current standards in SoC verification. UVM offers general conventions and ready building blocks for quick development of well-constructed and reusable verification environments on top of SystemVerilog language. Over 70% of ASIC verification in the industry is already done with UVM and the growth still continues [1].

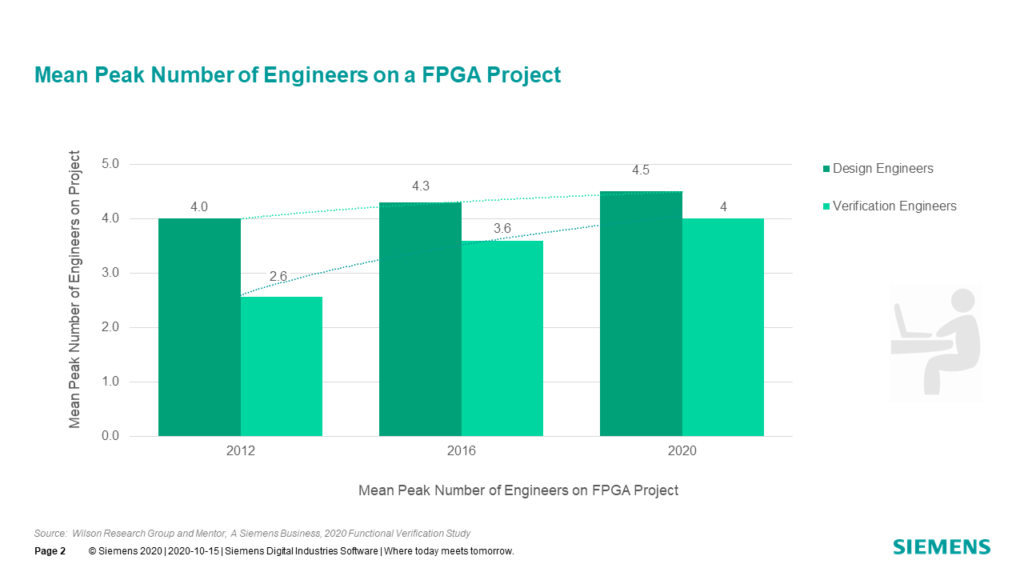

A recent study shows, that despite the increased productivity offered by UVM, the demand for skilled verification engineers is still growing [2]. Mastering SystemVerilog and UVM will be an attractive addition to your skill portfolio.

PREREQUISITES You should have taken an elementary course on digital logic design and a course on register-transfer level (RTL) design and coding, or acquired equivalent skills. Also, some experience in object-oriented programming is recommended. If you have created a simple testbench in VHDL language and know the keywords class, object, and constructor from Python or C++, you will probably do fine!

COURSE CONTENTS AND ORGANIZATION The course will teach you:

* Motivation for SoC verification,

* The design and verification oriented sides of SystemVerilog language, and

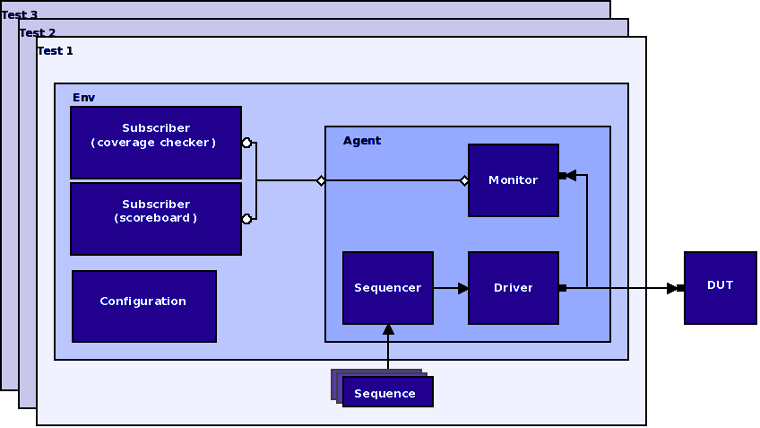

* UVM environment and test design.

The course consists of lectures, student seminar presentations and laboratory exercises. In the labs, you will create your own UVM environment and a coverage driven constrained random test for finding bugs in misbehaving designs. The course can be included in the master’s and post-graduate curriculum (5 credit points).

Sign up today to COMP.530-02 Verification with UVM and be quick, since we can accommodate at most 30 students.

If you have questions, contact arto.oinonen@tuni.fi

[1] Foster, H. “The 2018 Wilson Research Group Functional Verification Study”. Verification Horizons Blog (2019). Available: https://blogs.sw.siemens.com/verificationhorizons/2019/02/14/part-10-the-2018-wilson-research-group-functional-verification-study/

[2] Foster, H. “The 2020 Wilson Research Group Functional Verification Study”. Verification Horizons Blog (2020). Available: https://blogs.sw.siemens.com/verificationhorizons/2020/11/18/part-3-the-2020-wilson-research-group-functional-verification-study/