PREREQUISITES You should have taken an elementary course on digital logic design and a course on register-transfer level (RTL) design and coding, or acquired equivalent skills.

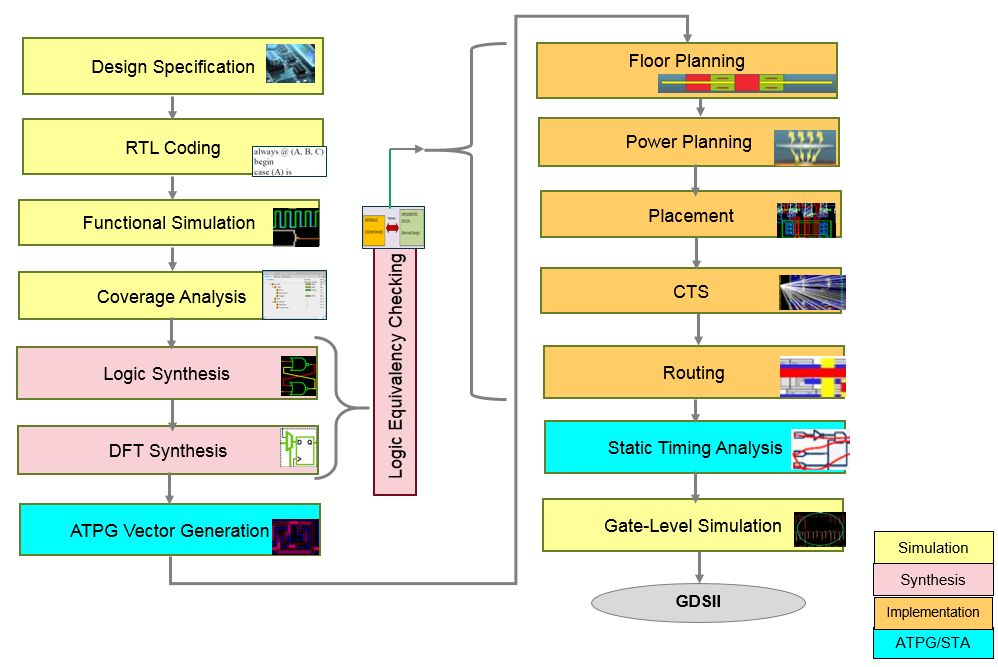

COURSE CONTENTS AND ORGANIZATION The course will teach you the complete design and verification flow, starting from RTL code and ending in physical IC layout, using Cadence tools, such as Genus and Innovus. The course consists of introductory lectures and laboratory exercises. An overview of the design flow and tools is given in instructor-lead sessions after which students can deepen their learning with online course modules. The course can be included in the master’s and post-graduate curriculum (2.0 credit points). If you are not a degree student of the university, you will have to apply for a fixed-term study right from the university to participate in the course.

Sign up today to TIE-11206 2019-02, but at the latest by November 30 2019, since we can accommodate at most 30 students.

If you have questions, contact arto.perttula@tuni.fi